OVERVIEW

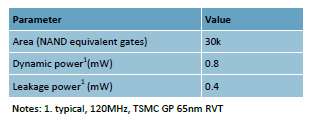

The AptCore ACR1 cores are fully programmable Digital Signal Processor units optimised for radar applications. Using an AptCore ACR1 DSP core reduces the size, power consumption and cost of the radar system.

The AptCore ACR1 uses patented techniques to efficiently perform the operations that are required in automotive radar processing:

- Complex FFT processing

- Optimised Real FFT processing

- Vector Multiplication (e.g. Windowing)

- Multiply Accumulate (e.g. Down sampling)

- Matrix Transpose for 2D FFTs

- Spike suppression for interference mitigation

- Magnitude of complex values

- Averaging and peak detection for CFAR detection

- Designed with full requirements traceability and failure analysis for easy integration into a safety critical design flow

The FFT efficiency is close to 100% as compared to the 30-40% maximum FFT efficiency of standard DSPs. This makes the ACR1 a much smaller and lower power solution. The internal data path allows for highly efficient 2D transpose and bit reverse reorder operations, which can be combined with vector multiply and multiply accumulate operations, giving further performance and efficiency gains.

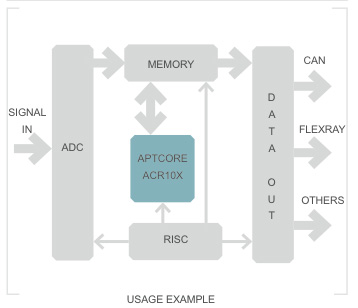

The AptCore ACR1 can be used alongside an industry standard RISC processor as a radar signal processing accelerator. Software development then uses the RISC’s standard toolchain, and employs AptCore’s DSP libraries to access ACR1 functionality.

The AptCore ACR1 is controlled using API calls sent over the system bus to a slave interface. Data is transferred to and from internal data memories via a master interface, with a double buffering option to allow the AptCore compute units to operate in parallel with data capture from ADCs.

BENEFITS:

- Greatly reduces system power – highest efficiency processor solution for radar

- Flexible solution – fully programmable via software

- Lowers unit cost – smallest size solution

- Easy to integrate – compatible with industry standard RISCs

- Rapid development facilitated through familiar programming environments

- Tailored to your requirements – highly configurable, fully scalable solution

FEATURES:

- Real or complex data can be processed efficiently

- Unique architecture for optimum efficiency

- AXI interfaces

- Reliability features for safety critical design

- AptCore Radar function library for easy programming

- Reliability features for safety critical design

DESIGN OPTIONS:

- Number of Cores

- Data width

- Integer or block scaled fixed point

- Maximum FFT length

- Double buffering for parallel data acquisition with processing

FFT PERFORMANCE

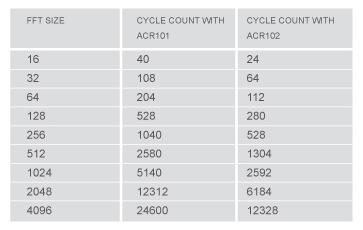

The table below shows the cycle count versus FFT length for ACR101 (single core) and ACR102 (dual core) processors. Clock speed used is dependent on target technology and performance requirements. For higher performance requirements, more cores can be added – please contact us for more information.

EXAMPLE

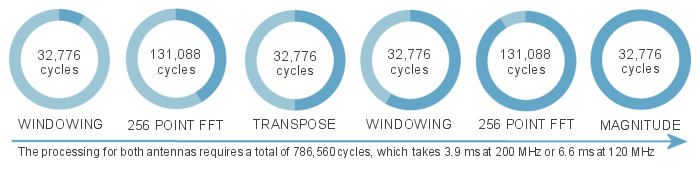

A radar system captures 256 sweeps of 256 points from two antennas. The samples are processed for range and velocity using a 2D complex Fourier transform. The phase of the detections from each antenna are compared to determine the direction.

The cycle counts in the above example are for the ACR102. Peak detection and local averaging can be included in the magnitude operation to accelerate Constant False Alarm Rate (CFAR) detection. Saturation caused by Continuous Wave (CW) interference may be suppressed by the core as the samples are received.

For a more detailed explanation of range-Doppler processing, see our paper EuRAD paper: An Optimised Processor for FMCW Radar